#### Lowering the Environmental Impact of High-k and

#### **Metal Gate-Stack Surface Preparation Processes**

(Task Number: 425.028)

#### <u>PIs</u>

- Yoshio Nishi, Electrical Engineering, Stanford

- Srini Raghavan, Materials Science and Engineering, U of Arizona

- Bert Vermeire, Electrical Engineering, Arizona State University

- Farhang Shadman, Chemical Engineering, U of Arizona

#### **Co-PIs:**

- Manish Keswani, Materials Science and Engineering, U of Arizona

- Jun Yan, Chemical Engineering, U of Arizona (now with Lam Research)

- Omid Mahdavi, MFC Facilities Manager, U of Arizona

#### **Students:**

- Kedar Dhane, PhD, Chemical Engineering, U of Arizona (now with Intel)

- Gaurav Thareja, PhD, Electrical Engineering, Stanford (now with Intel)

- Davoud Zamani, PhD candidate, Chemical Engineering, U of Arizona

- Michael McBride, Undergraduate Assistant, Chem. Eng., U of Arizona

#### **Cost Sharing:**

- \$50k from Stanford CIS

- \$50k from WSP

# **Objectives**

- Development of a wet etch method to lower fluoride consumption during etching of hafnium based high-k materials

- Investigate the rinsing fundamentals of micro and nano structures in hafnium based high-k materials; develop new technologies (hardware, process models, and process recipes) to reduce water and energy usage during these processes.

## **Subtasks 1 and 2**

- A wet etch method to reduce fluoride consumption during etching of high-k.

- Reduction of water and energy usage for rinse after high-k etch.

#### **ESH Gain in Etching of Hafnium Silicate**

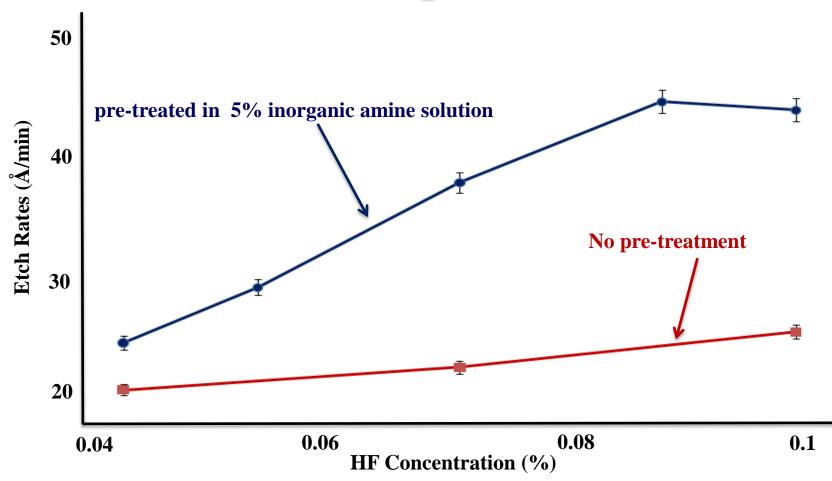

# Reductive pretreatment of hafnium silicate ( $HfSi0_{0.74}O_{3.42}$ ) in 5% inorganic amine solution improves the etch rate in 1:1000 $HF:H_2O$ .

# **Rinsing Dynamics of Hafnium-Based High-K Micro and Nano Structures in Single-Wafer Cleaning Tools**

### **Method of Approach**

- Apply the novel ECRS metrology method for in-situ and real-time monitoring of the hafnium-based high-*k* surfaces in single wafer tools.

- Combine metrology with process modeling to identify the controlling steps (bottlenecks) in the cleaning and rinsing of micro and nano structures for hafnium based high-*k* materials.

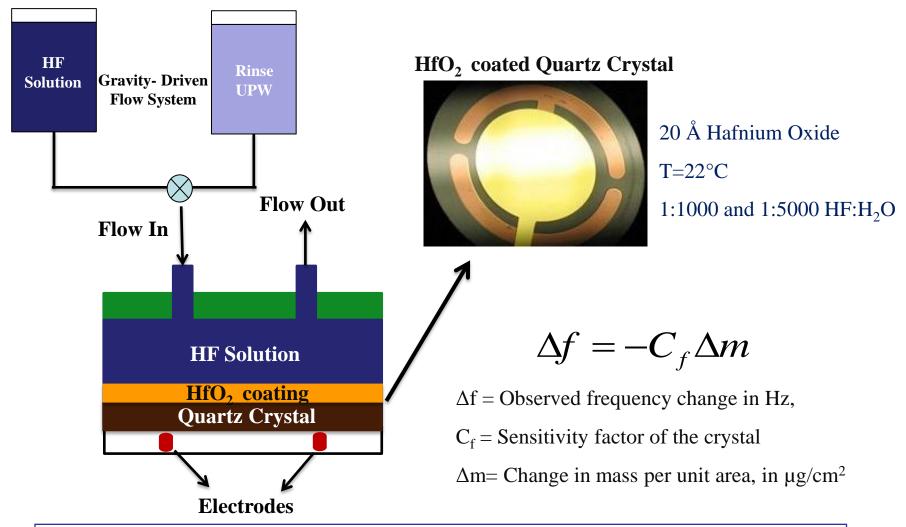

## **Determining the Process Parameters Experimental Set Up**

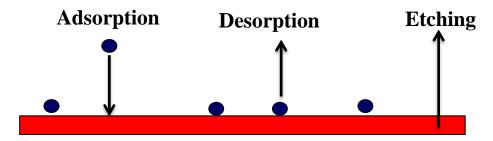

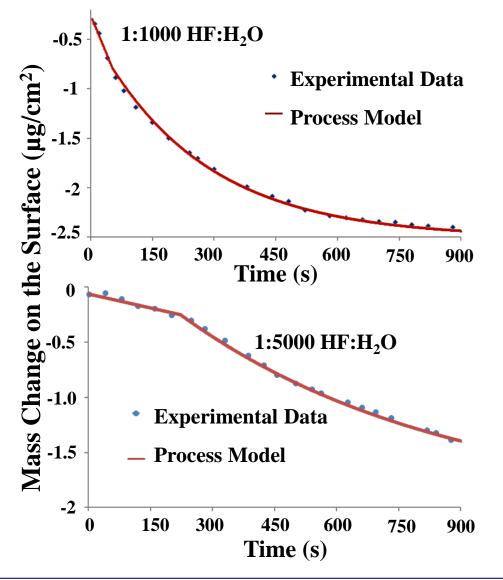

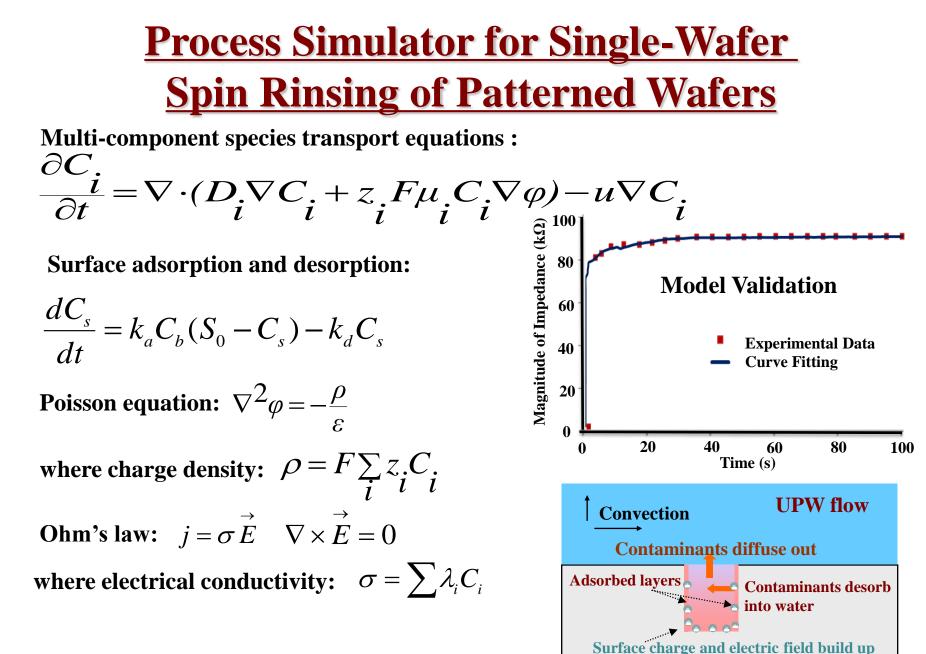

### **Process Model for HF /High-k Interactions**

k<sub>a</sub>: Adsorption Rate Coefficient

k<sub>d</sub>: Desorption Rate Coefficient

k<sub>e</sub>: Etching Rate Coefficient

$$\frac{dC_s}{dt} = k_a C_b (S_0 - S_2 - C_s) - k_d (C_s)$$

adsorption rate of HF desorption rate of HF

$$\frac{dS_2}{dt} = k_p [H^+] (S_0 - S_2 - C_s) - k_e C_b S_2$$

$$\frac{1}{A} \frac{dM}{dt} = (MW_{HF}) \frac{dC_s}{dt} + (MW_{H^+}) \frac{dS_2}{dt}$$

$$- (MW_{HFO_2}) k_e C_b S_2$$

etching rate of HfO<sub>2</sub>

#### **Analysis of the Experimental Data**

- Adsorption Rate Coefficient: 1000 (lit/mol.s)

- Desorption Rate Coefficient : 0.1 (1/s)

- Etching Rate Coefficient : 1200 (lit/mol.s)

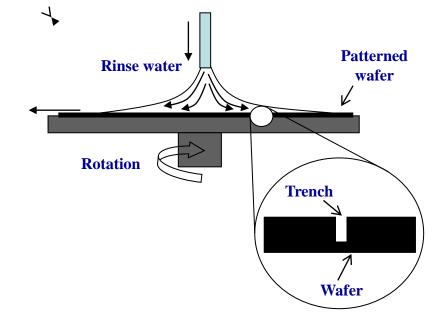

# **Testbed for Single-Wafer Spin Rinsing and Drying**

**Spin Rinse Testbed**

- A single wafer tool equipped with ECRS is designed and set up.

- Combination of experiments and process model is used to study the effect of various process parameters.

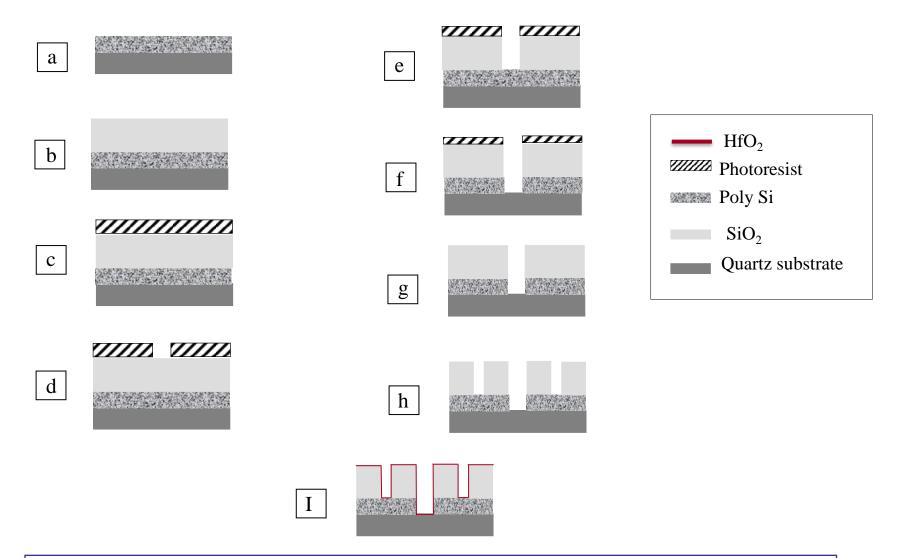

### **Fabrication of Test Wafer and In-Situ Sensor (ECRS)**

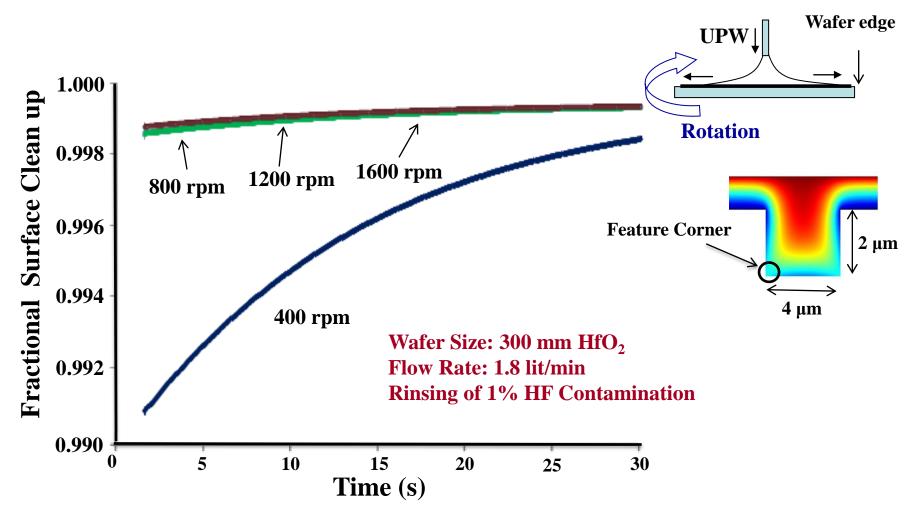

### **Effect of Rotation Speed in Single-Wafer Tools**

The results indicate an increase in rinsing efficiency as the spin rate increases. However, increasing the spin rate beyond 800 rpm has no further impact on the rinse efficiency.

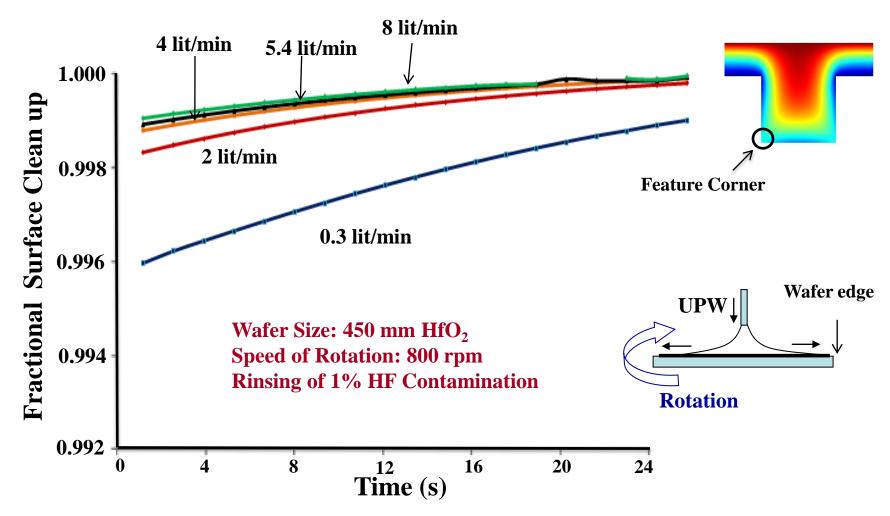

#### **Effect of Flow Rate in Single-Wafer Tools**

The results indicate an increase in rinsing efficiency as the flow rate increases. Increasing the flow rate beyond 4 lit/min has lower impact on the rinse efficiency.

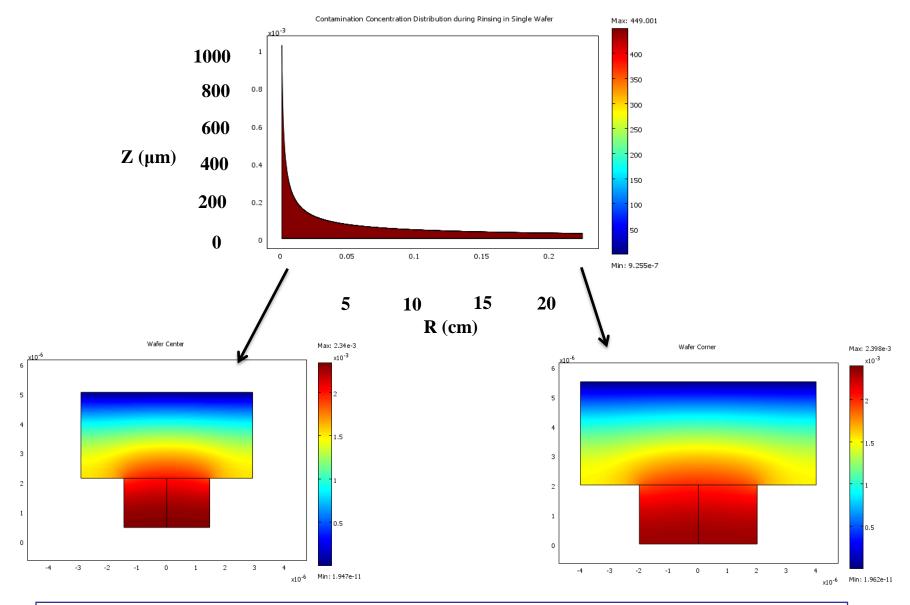

#### **Residue Concentration Distribution During Rinsing**

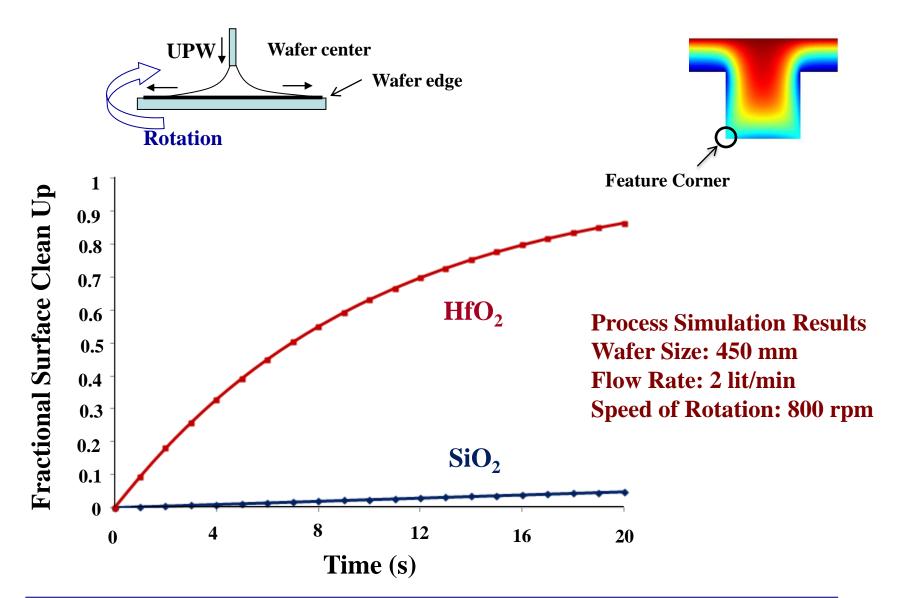

## **<u>HfO<sub>2</sub></u>** and SiO<sub>2</sub> Surface Cleaning Comparison

SRC/SEMATECH Engineering Research Center for Environmentally Benign Semiconductor Manufacturing

# **Summary and Conclusions**

- An experimental method was developed to determine the fundamental mechanism and process parameters in rinsing and cleaning of high-k materials and nano-structures.

- The effects of key process parameters, including the speed of rotation, flow rate, and wafer size were investigated.

- A comprehensive rinse process simulator was developed and tested. The simulator can be used to optimize and lower water and energy usage.

# <u>Industrial Interactions and</u> <u>Technology Transfer</u>

- Interactions with ASM (Eric Shero and Eric Liu) for preparation of high-k wafers

- Interactions with Freescale and Environmental Metrology Corp (EMC) for testing of new low-water rinse recipes

- Interactions with Sematech (Joel Barnett) for high-k etching and development of the cleaning/rinsing recipe/process

- Technical interactions with Kedar Dhane and Jun Yan on application of the rinse model and metrology techniques.

# **Publications and Presentations**

•Zamani, D., Mahdavi, O., McBride, M., Dhane, K, Shadman, F., "Cleaning and Rinsing of Hafnium based High-K Micro and Nano Structures in Single-Wafer Cleaning Tools" ready to submit to AIChE Journal.

•Zamani, D., Keswani, M., Mahdavi, O., Yan, J., Raghavan, S., Shadman, F., "Dynamics of Interactions between HF and Hafnium Oxide during Surface Preparation of High-K Dielectrics" in press at IEEE Transactions and Semiconductor Manufacturing.

•Zamani, D., Keswani, M., Yan, J., Raghavan, S., Shadman, F., "Determining the Fundamental Kinetic Parameters for Rinsing and Cleaning of Hafnium-Based High-k Materials" ECS Transactions, 41 (5) 45-50 (2011).

•Zamani, D., Yan, J., Mahdavi, O., Zhang, X., Vermeire, B., Shadman, F., "Application of Novel On-Line Metrology Technique to Reduce Water and Energy Usage during Surface Preparation of Patterned Wafers in Single – Wafer Tools" Invited Paper for SRC-TECHCON, Presentation –Poster, September 2011.

•Zamani, D., Yan, J., Keswani, M., Mahdavi, O., Raghavan, S., Shadman, F., "Environmentally Friendly Chemicals for Patterning of Hafnium Based High-K Materials and Rinsing in Single-Wafer Cleaning Tools" SRC-TECHCON, Presentation-Poster, September 2011.

•Zamani, D., Thareja, G., Yan, J., Keswani, M., Mahdavi, O., Dhane, K., Nishi, Y., Raghavan, S., Vermeire, B., Shadman, F., "Lowering the Environmental Impact of High-k and Metal Gate-Stack Surface Preparation Processes" Annual Site Review, SRC/Sematech Engineering Research Center for Environmentally Benign Semiconductor Manufacturing, Presentation –Poster, March 2011.

•Dhane, K., Han, J., Yan, J., Mahdavi, O., Zamani, D., Vermeire, B., Shadman, F., "Dynamics of Cleaning and Rinsing of Micro and Nano Structures in Single – Wafer Cleaning Tools" IEEE Transactions and Semiconductor Manufacturing, Vol. 24, NO. 1, February 2011.