#### Challenges and Opportunities for Future Nanoelectronic Devices

#### Ken Uchida

**Toshiba Corporation / Stanford University**

ERC TeleSeminar, April 28, 2005

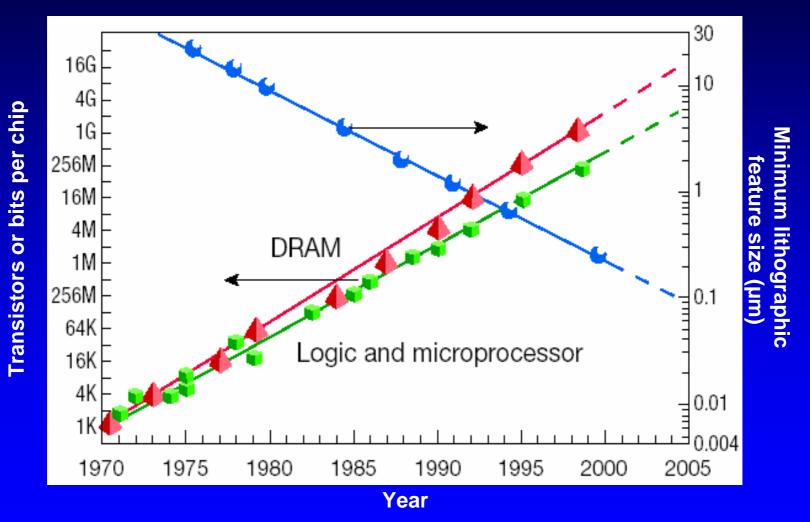

### Scaling Trend of MOSFETs - General -

A. I. Kingon et al., Nature 406, 1032 (2000).

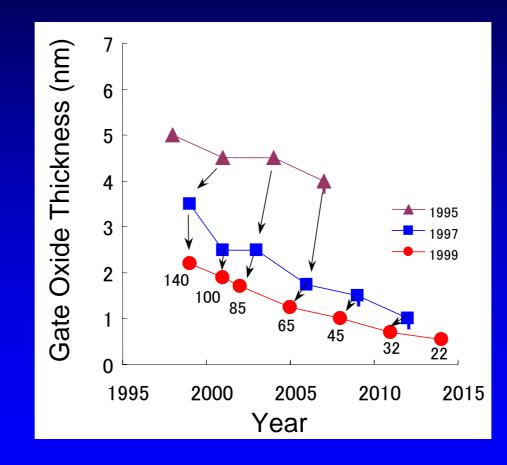

#### Scaling Trend of MOSFETs - Gate Oxide Thickness -

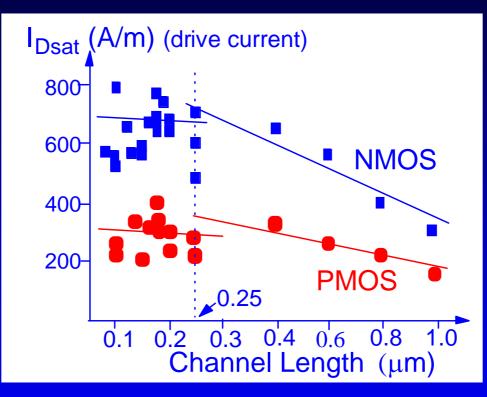

#### **Saturation of Tr. Performance**

Changhoon Choi, PhD Thesis in Dutton Group, Stanford Univ., 2002

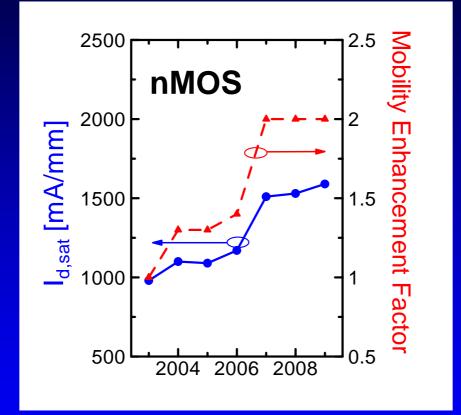

#### Introduction of New Technology

#### **Paradigm Change (I)**

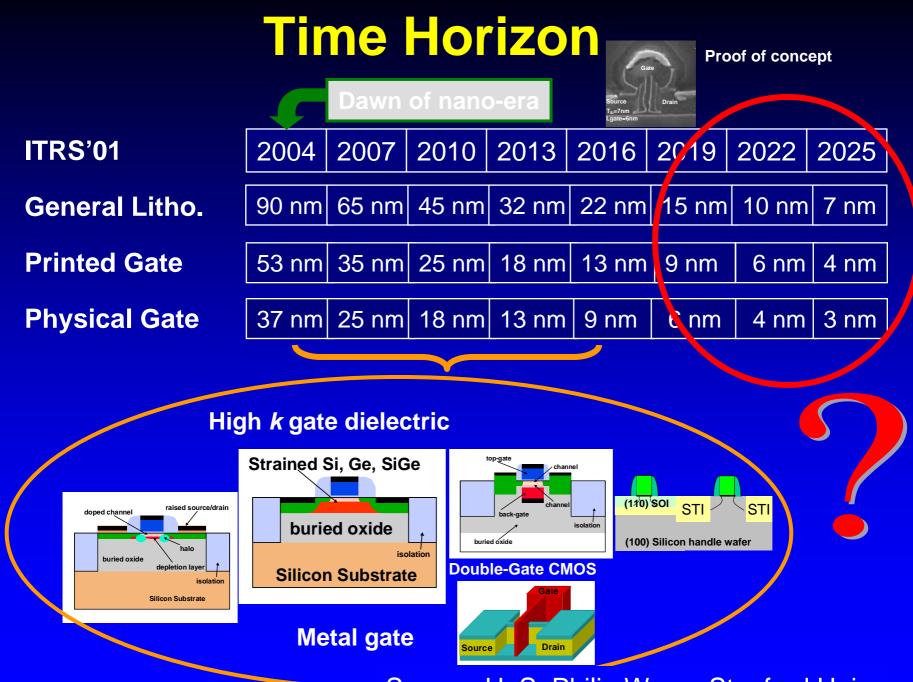

#### Scaling Technology Node

WAS Scaling Device Sizes

IS Scaling Device Sizes

+

Introducing New Technology

High-κ, Stressed Channel, Ultrathin-body SOI, Schottky S/D etc.

#### Innovation Overtakes Scaling in Driving Performance

- Innovation (invention) will increasingly dominate performance gains

- Scheduled "invention" is now the majority component in all plans

- **IBM Transistor Performance Improvement** Gain by Traditional Scaling Gain by Innovation 100 80 **Relative % Improvement** 60 40 500 90 250 180 130 nm 350 nm 65 20 nm nm nm nm nm 0 **CMOS6X** CMOS5X **CMOS7S-SOI** CMOS8S2 S0SOMC CMOS10S CMOS11S

- Risk has increased significantly

#### Source: H. S. Philip Wong, Stanford Univ. 7

Source: H. S. Philip Wong, Stanford Univ. 8

### **Today's Topic**

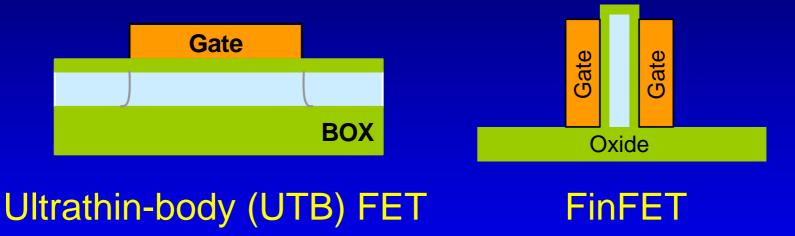

#### Ultrathin-body (UTB) MOSFETs

- ✓ Better Short Channel Immunity

- ✓ Lower Parasitic Capcitance

- ✓ Reduced S/D Leakage

- ✓ Lower Substrate Impurity Conc.

#### Schottky Source/Drain MOSFETs

- ✓ Better Short Channel Immunity

- ✓ Lower Parasitic Resistance

- ✓ Abrupt Junction

#### **Requirement for LSI**

#### High Speed and Low Power

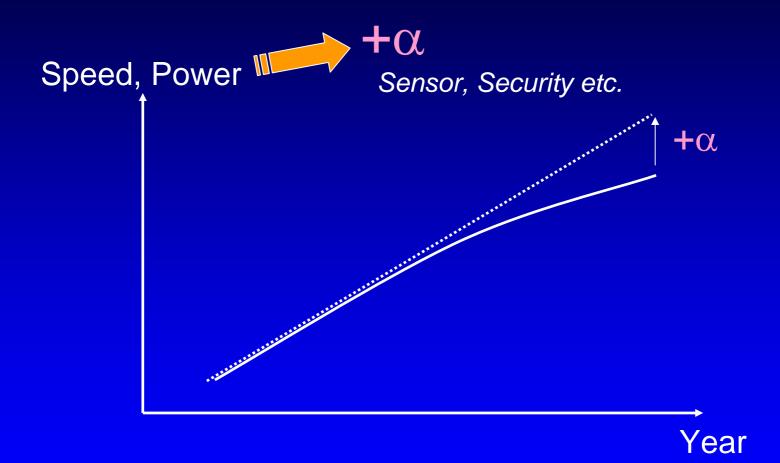

Yes, it has been required and will be required in future as well. If we have high-performance LSI, we can do almost everything, such as complicated scientific calculation, MPEG encode, decode, game.

However, in ubiquitous era, requirements for LSI will be changed. LSI should <u>communicate</u> with environments and users <u>securely</u>.

#### Paradigm Change (II)

# Single-Electron Devices for Security Applications

### **Ultrathin-body MOSFETs**

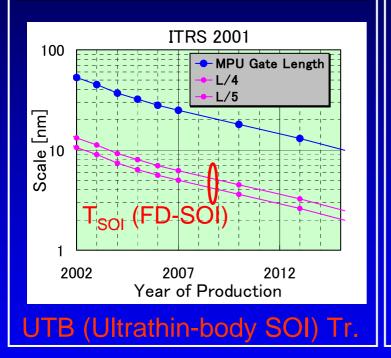

#### **UTB MOSFETs**

T<sub>SOI</sub> of less than 10nm is required.

# Wavefunction width is larger than 10nm

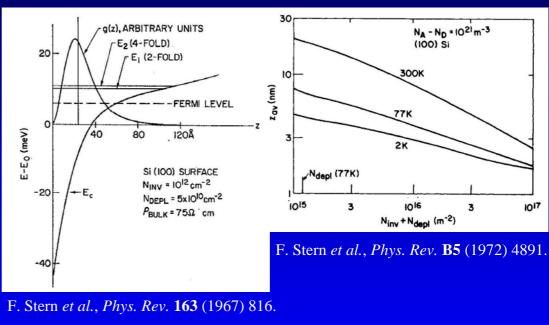

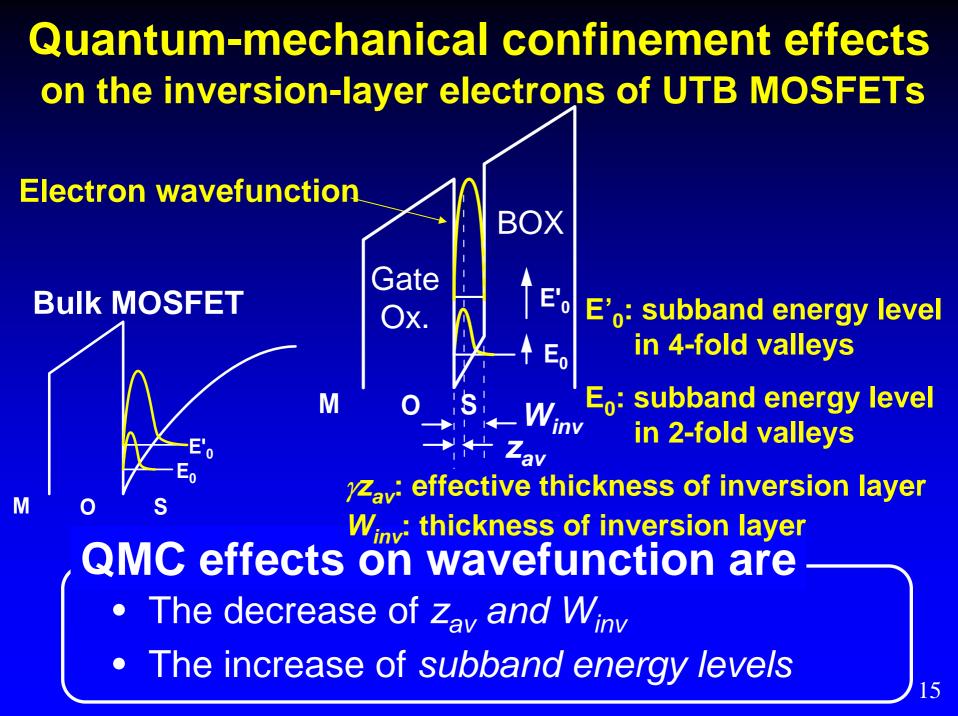

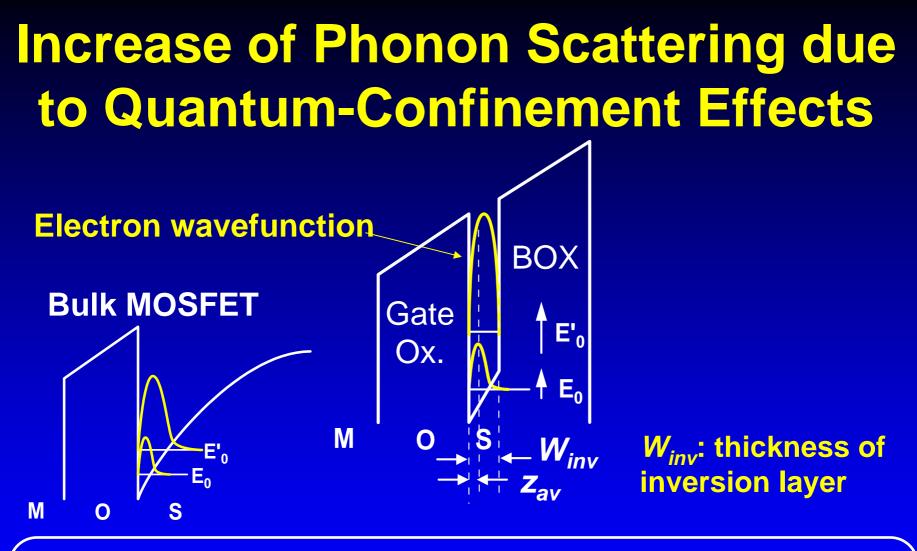

#### Impact of quantum-mechanical effects on the characteristics of UTB MOSFETs

#### As $W_{inv}$ and $z_{av}$ decrease, we can expect ...

- the decrease of electron mobility  $\mu_{eff}$ .  $\mu_{ac} \propto |W_{inv}| = \mu_{ac}$ : acoustic phonon-limited mobility

- the increase of Inversion-layer capacitance  $C_{inv}$ .

$C_{inv} = \varepsilon_{Si} / \gamma |z_{av}|$  A. Hartstein, PRB38, p1235, 1988.

• the increase of Gate-channel capacitance  $C_{gc}$ .

$1/C_{gc} = 1/C_{ox} + 1/C_{inv}$

As  $E_n$  and  $E'_n$  increase, we can expect ...

• the increase of  $V_{th}$ .

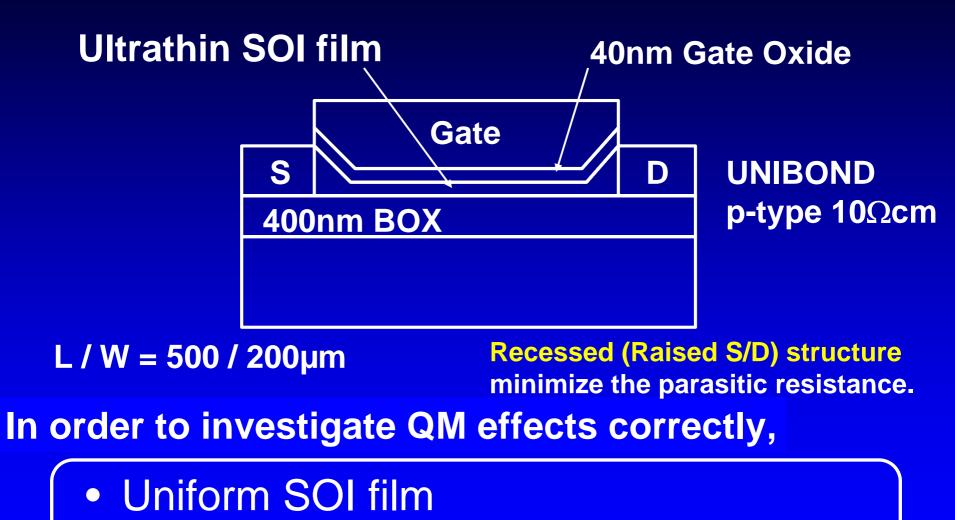

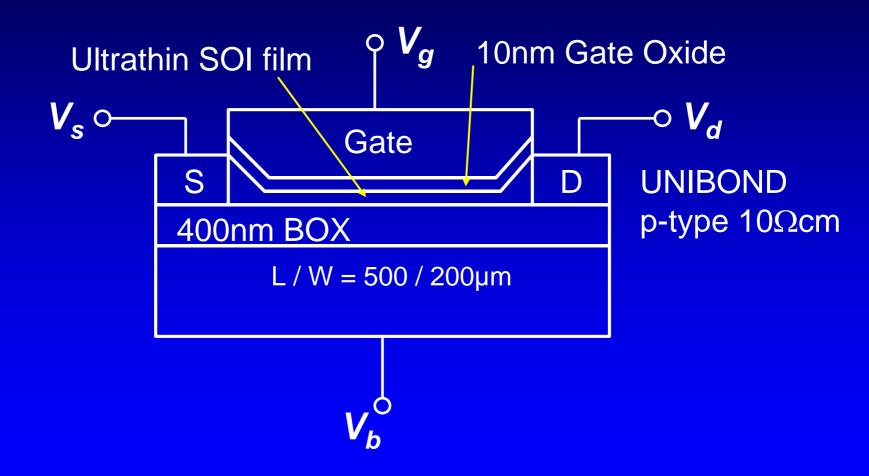

# **Device Structure**

are required

17

• Stress-free SOI film

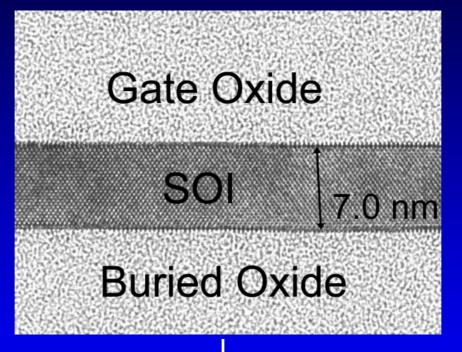

#### Thickness & Uniformity Evaluation TEM Observation

Cross section of the channel

• Ultrathin (7.0 nm ~ 12.4 nm)

Uniform

SOI films are successfully fabricated.

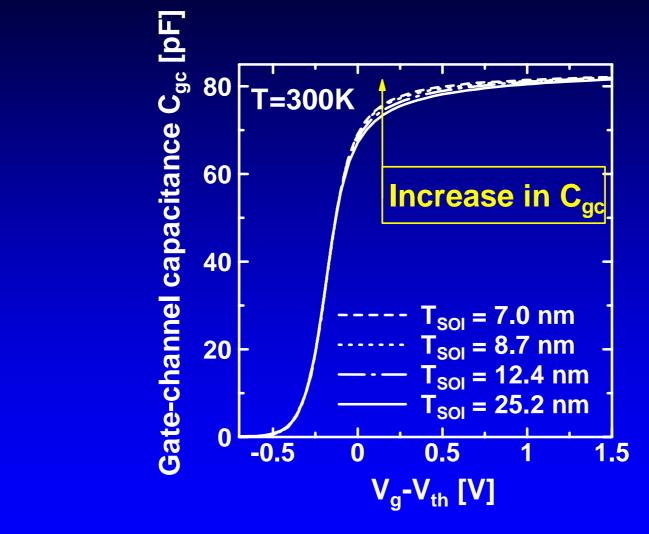

# $C_{g}$ - $V_{g}$ characteristics for various $T_{SOI}$

# $C_{gc}$ increases as $T_{SOI}$ decreases.

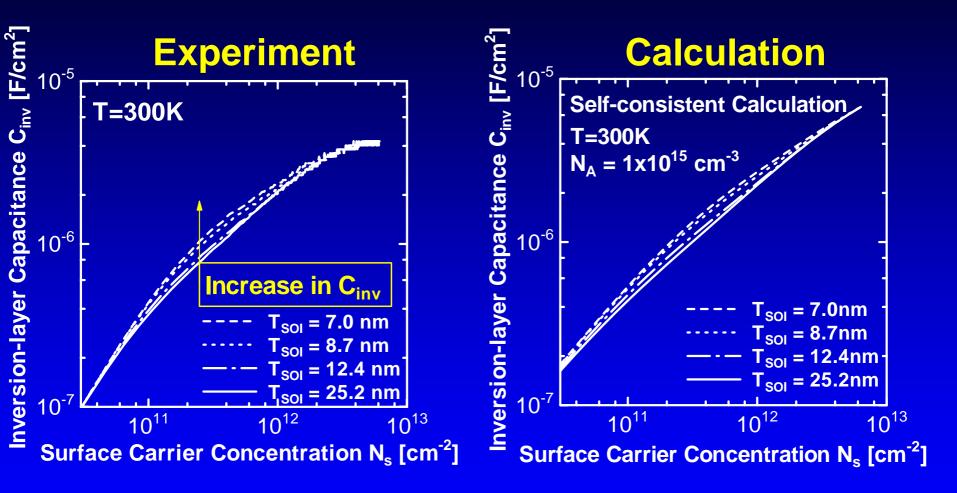

### $C_{inv}$ - $N_s$ Characteristics for various $T_{SOI}$

Experimental and Calculated results are consistent. The increase of  $C_{inv}$  and  $C_{gc}$  is due to QM confinement<sub>20</sub>

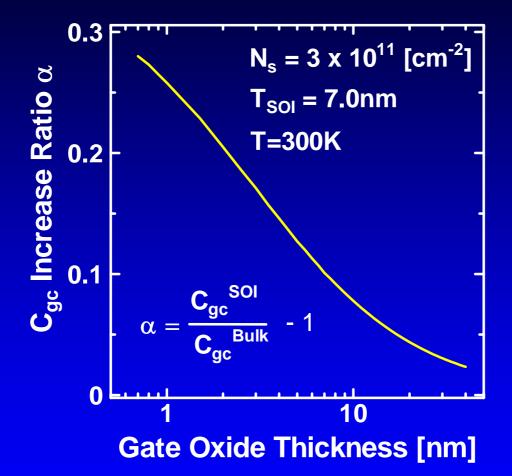

# $C_{gc}$ Increase ratio as a function of $T_{SOI}$

$C_{gc}$  of 7nm UTB MOSFETs is 25% greater than that of bulk MOSFETs in 1nm T<sub>ox</sub> regime.

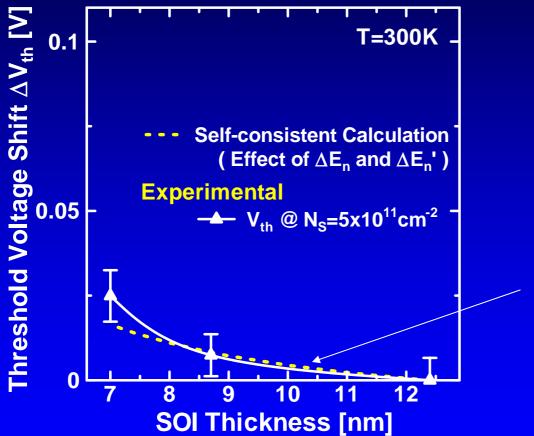

# V<sub>th</sub> determined from C-V

Agree well !

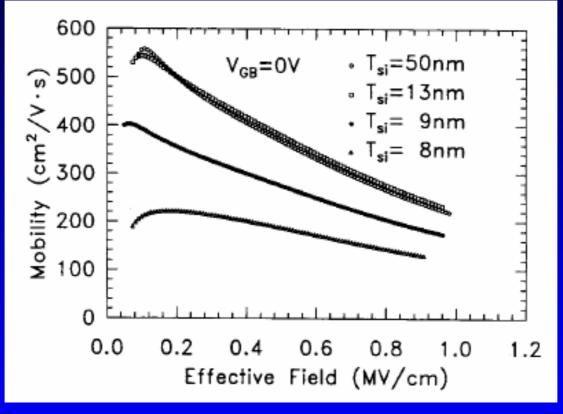

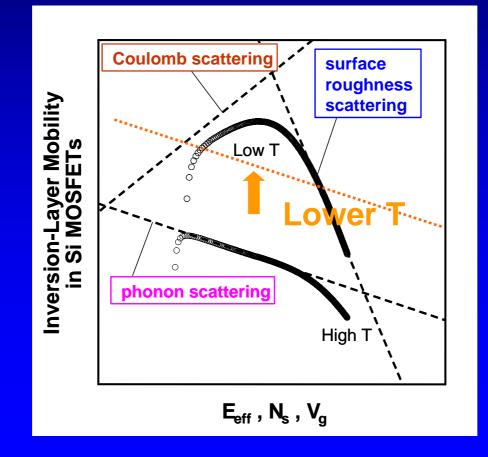

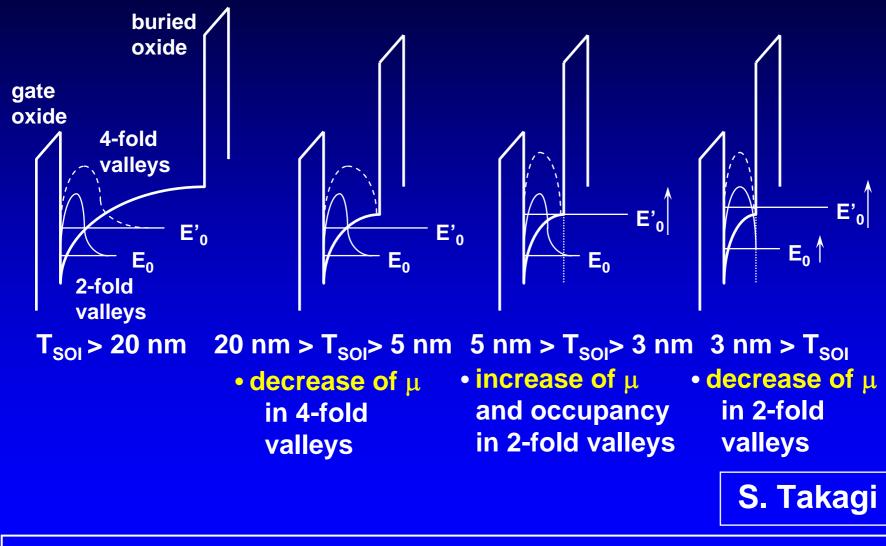

#### Mobility Degradation in Ultrathin-body SOI MOSFETs

J.-H. Choi, EDL 16 (1995) 527.

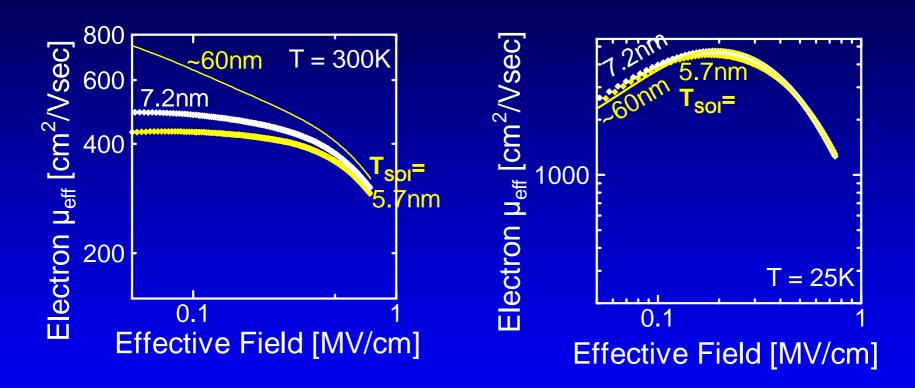

Mobility degradation have been observed in SOI MOSFETs with  $T_{SOI}$  of less than ~20nm.

Electron mobility decreases in thinner  $T_{SOI}$ .  $\mu_{ac} \propto |W_{inv}| \qquad \mu_{ac}$ : acoustic phonon-limited mobility  $\tau_{SOI}^{l}$  S. Takagi, IEDM97, p219.

# Hypothesis: Mobility degradation is due to phonon scattering increase.

# Verification: Low temperature measurement of mobility

### **Device Structure**

#### **Temperature Dependence**

Mobility reduction in UTB MOSFETs with  $T_{SOI}$  of greater than 5nm is due to the increase of phonon scattering.

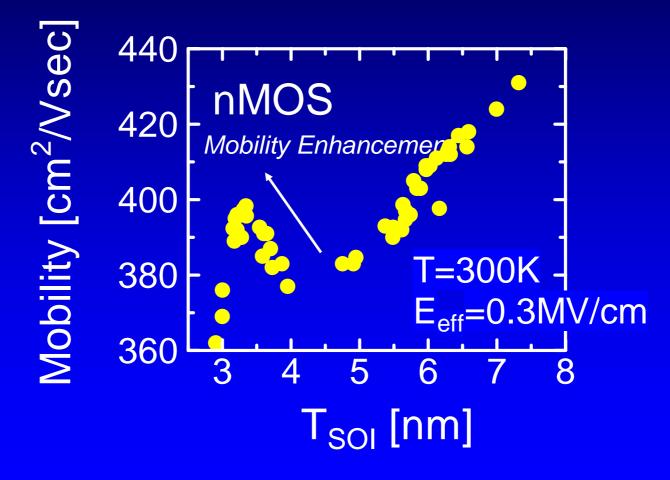

#### Mobility Increase with a decrease in T<sub>sol</sub>

Mobility Increase is expected in T<sub>SOI</sub> range from 3 to 5nm.

# **Electron Mobility as a function of T<sub>SOI</sub>**

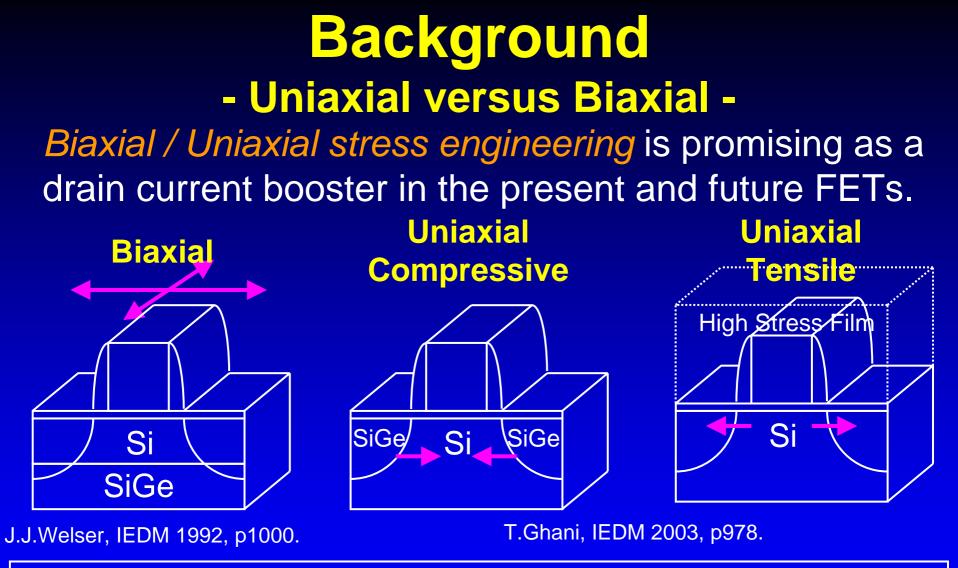

The advantages of biaxial (uniaxial) stress engineering over uniaxial (biaxial) stress engineering are not clear.

The effect of uniaxial stress on mobility is not clear.

#### Background (Cont'd) - UTB Structure -

MOSFETs utilizing ultrathin Si layers are promising as a 20nm-regime device structure.

The effectiveness of biaxial/uniaxial stress engineering in <u>Si films of less than 5nm</u> has not been clarified yet.

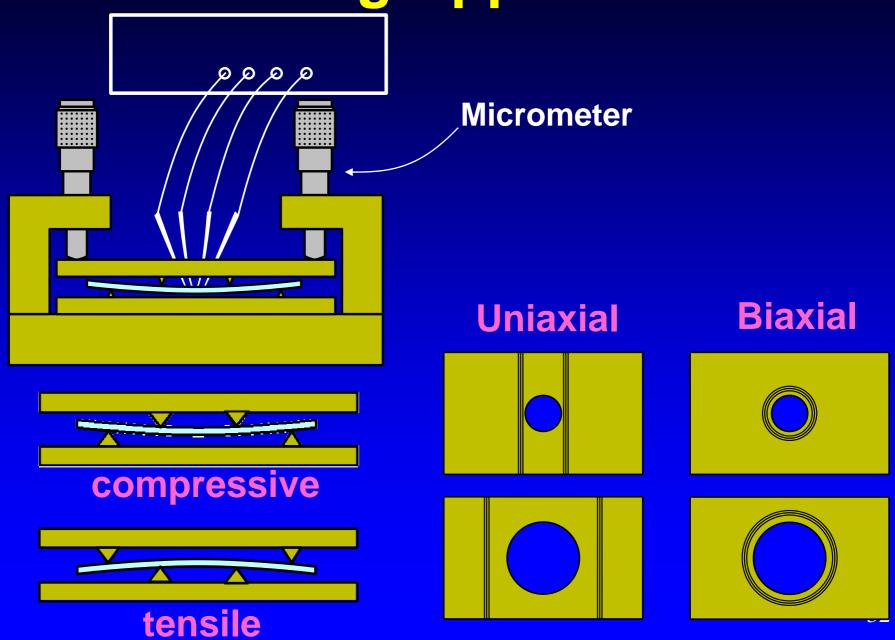

#### **Bending Apparatus**

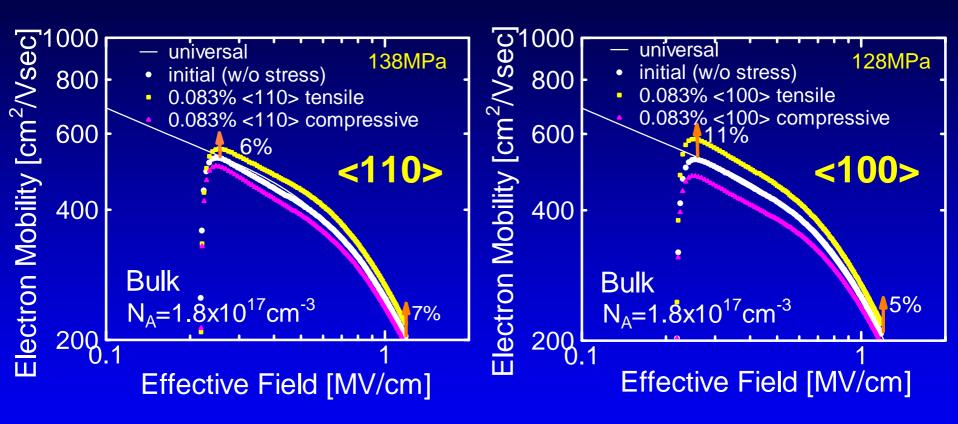

# **Electron Mobility**

Electron mobility enhancement is greater in <100> case than in <110> case.

# **Hole Mobility**

The hole mobility enhancement is much greater in <110> case than in <100> case.

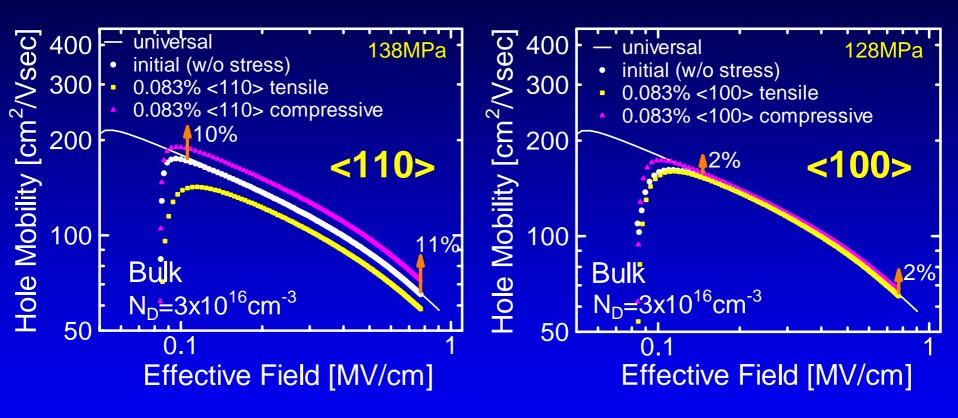

#### **Biaxial Tensile Stress**

The enhancement of electron mobility is better than that of <110> and <100> uniaxial tensile strained FETs under almost the same amount of strain. However, hole mobility enhancement cannot be observed due to the small amount of strain induced by bending.

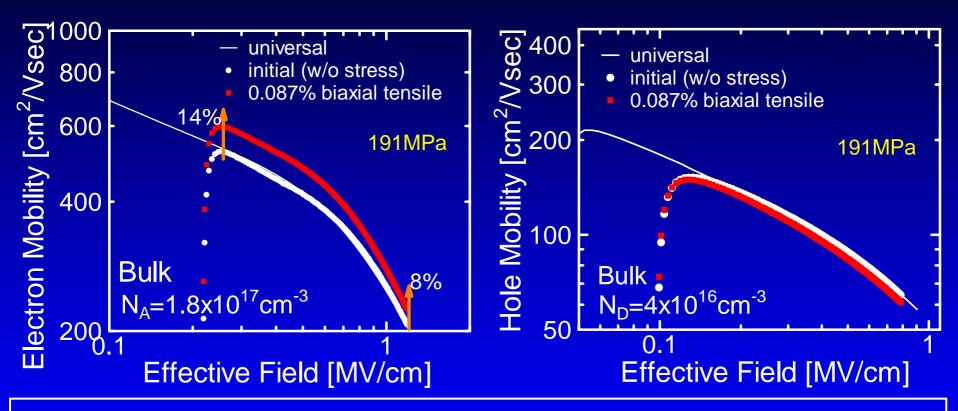

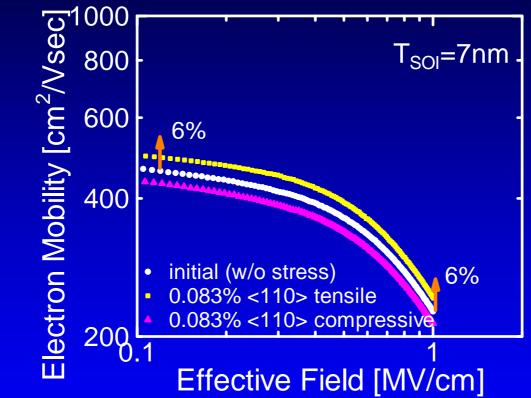

#### Effectiveness of Uniaxial Stress Engineering

It is demonstrated, for the first time, that uniaxial strain engineering is effective even in UTB MOSFETs with  $T_{SOI}$  of less than 10nm. The enhancement ratio is almost the same as that of bulk FETs.

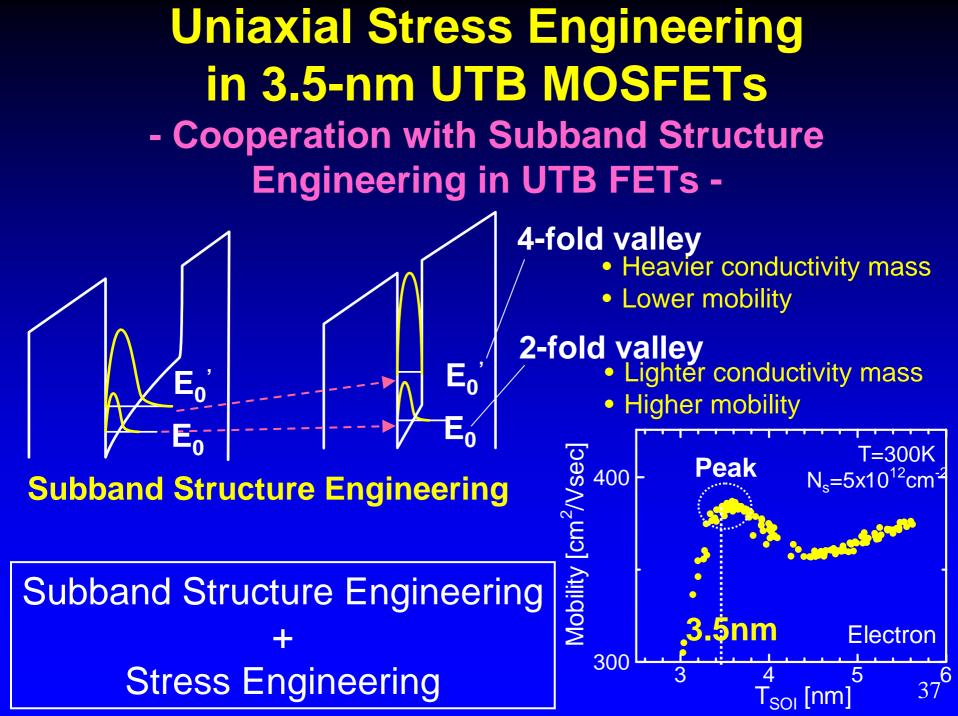

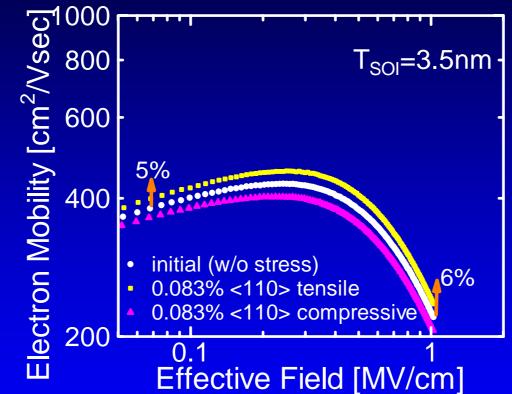

# Uniaxial Stress Effects in 3.5-nm UTB nMOSFETs

It is demonstrated that uniaxial strain engineering is still effective in UTB MOSFETs with  $T_{SOI}$  of less than 5nm, and can be used with subband structure engineering by TSOI optimization at the same time to enhance mobility. 38

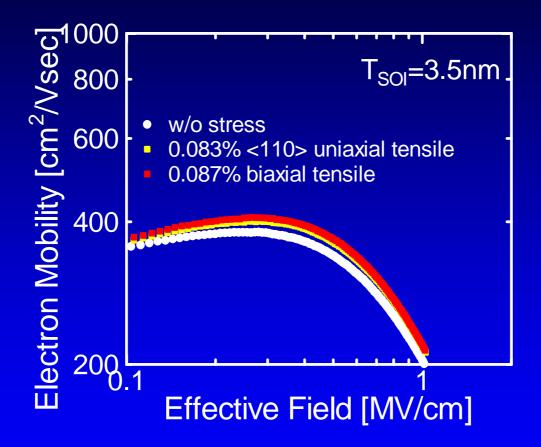

## Uniaxial versus Biaxial in 3.5-nm UTB nMOSFETs

It is demonstrated that the advantage of biaxial tensile strain over uniaxial tensile strain in terms of electron mobility becomes less in 3.5-nm UTB FETs.

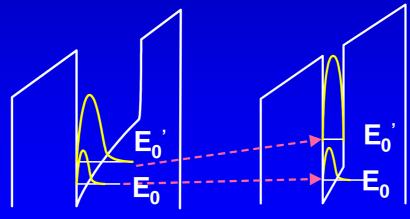

#### **Why Mobility Enhance?** Conventional Model: split of 2-fold and 4-fold valley $\Delta_6$ $\Delta_4$ (higher $\mu$ ) $\Delta E \propto \varepsilon$ $\Delta_2$ (lower $\mu$ ) In UTB MOSFETS,

the split of 2-fold and 4-fold valley already takes place.

The mobility enhancement in UTB MOSFETs cannot be simply explained by the conventional model.

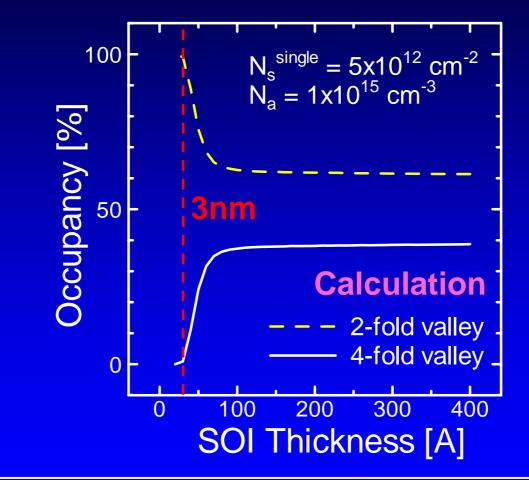

#### Occupancy of Electrons in 2-fold and 4-fold Valleys of UTB FETs

The occupancy of 2-fold valley becomes almost 100% if SOI thickness is less than 3nm.

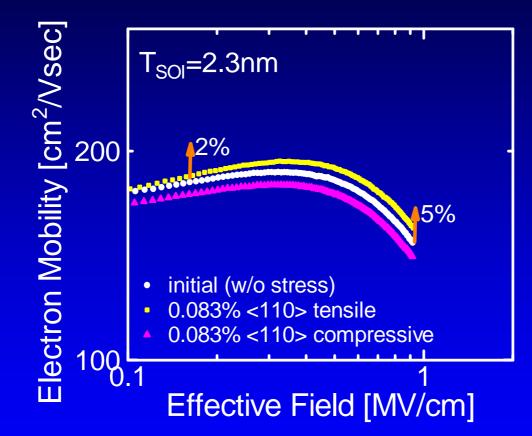

# Uniaxial Stress Effects in 2.3-nm UTB nMOSFETs

The electron mobility enhancement in this device is not due to the split of 2-fold and 4-fold valleys.

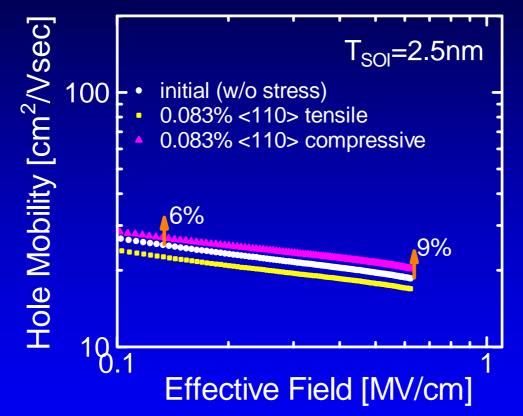

# Uniaxial Stress Effects in 2.5-nm UTB pMOSFETs

The hole mobility in UTB MOSFETs with  $T_{SOI}$  of less than 3nm is also increased by uniaxial stress engineering.

# Single Electron Device for Security Applications

### Introduction

#### In Ubiquitous Computing Era,

- A variety of services (*ticket service*, *e-commerce* etc.) will be provided on the basis of electrical authentication with wireless ubiquitous client (*RFID*, *non-contact Smart Cards* etc.).

- The security requirements for the ubiquitous client have been greatly increased in recent years.

Electric Money Password etc.

**Private Information**

**Mobile Client**

**Smart Card**

(IC Card)

Wireless Communication

Server

45

#### Introduction

# RNGs are essential components for electrical security systems.

- The security of modern cryptographic technique relies on <u>unpredictability</u> and <u>irreproducibility</u> of random numbers. (eg. digital secret key)

- Random numbers can be used to jumble inner electrical signals of mobile clients, and thus disturb bugging or tampering by intentional hackers.

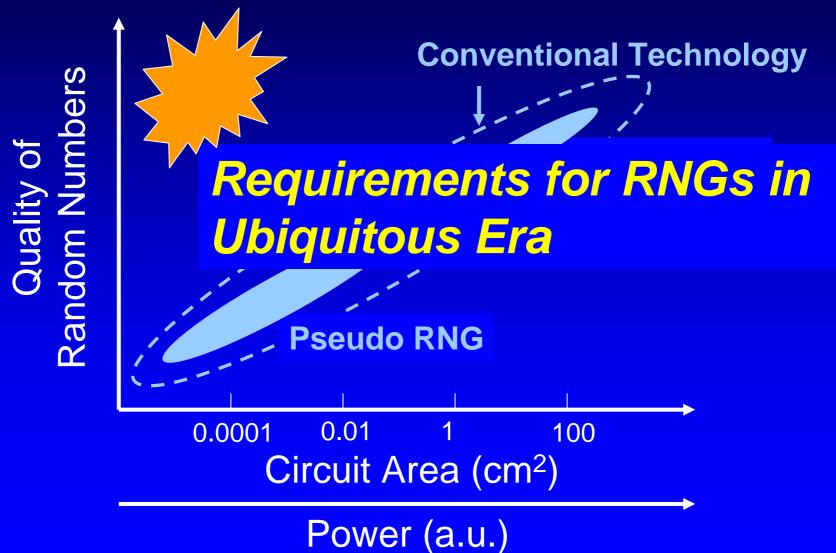

The realization of high-quality RNGs in a small area with low power consumption is strongly required for mobile client in ubiquitous era.

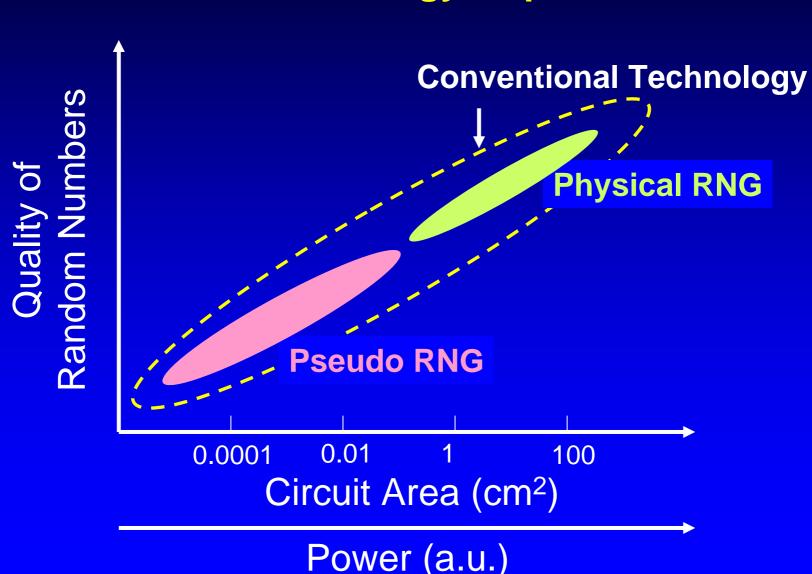

#### Introduction - Class of RNGs -

Pseudo RNG

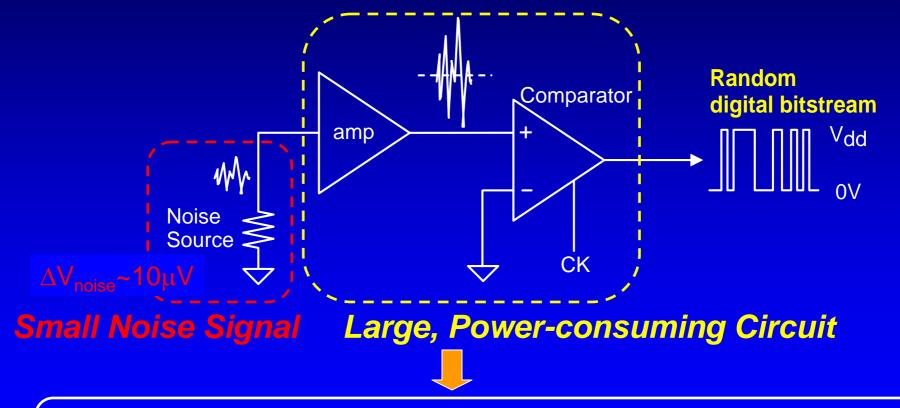

#### Introduction -Example of Physical RNG-

#### **Electrical RNGs based on Physical Phenomena**

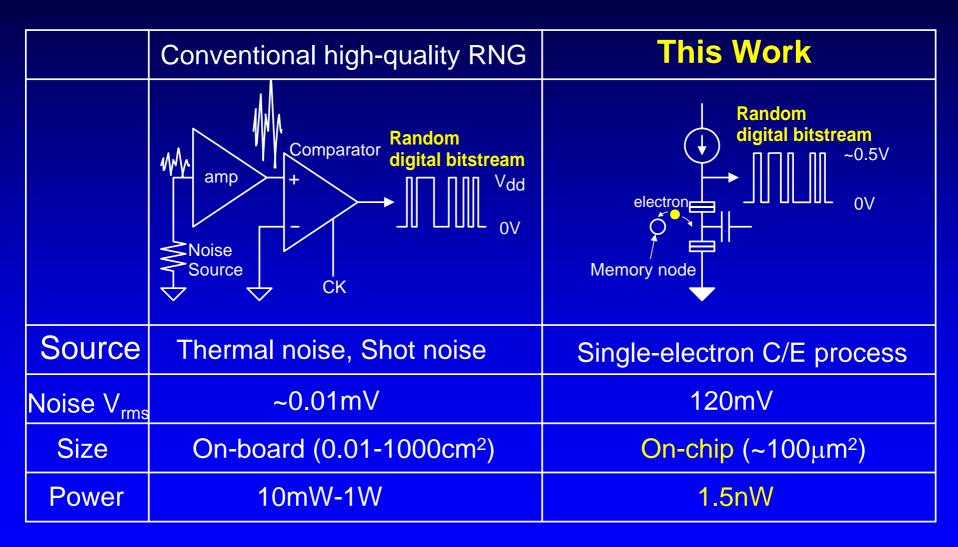

Present high-quality RNG is large, power-consuming circuit, and is not suitable for ubiquitous applications.

# -Pseudo RNG-

#### **Pseudo Random Number**

Pseudo random numbers are <u>digital sequences that</u> <u>have long correlation</u>, and can be regarded as "random numbers". They are generated by a certain <u>algorithm</u>, and therefore they are <u>reproducible</u> and <u>predictable</u>.

Pseudo RNGs cannot provide high security.

However, pseudo RNGs have small and low-power properties. Example of pseudo RNG

Linear Feedback Shift Resister (LFSR)

Four-bit LFSR

LFSRs are small digital circuits, but they were already hacked (see, J.A. Reed, *Cryptologia* 1 (1977) 20)!

#### Introduction -Technology Map-

#### Introduction -Technology Map-

# Objective

To realize high-quality, small and low-power RNGs Suitable for Secure Ubiquitous Computing Era In This Work,

- Propose the concept of single-electron RNG

- Justify whether the single-electron RNG is useful for generating high-quality random numbers in a small area with low power consumption or not.

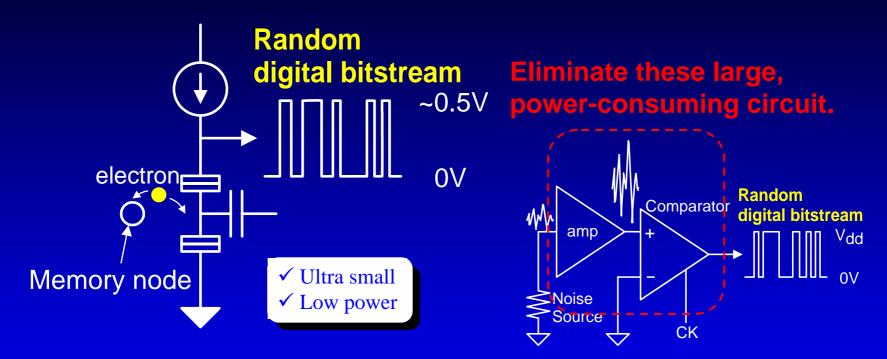

#### **Concept of Single-Electron RNG**

- Utilize stochastic single-electron capture/emission process to/from an electron pocket as physical seeds for random numbers.

- Detect single-electron capture/emission process with single-electron transistor.

#### Single-Electron RNG = SET + Single-Electron Pocket (Trap)

#### **Advantages of Single-Electron RNG**

Single-electron capture/emission processes change SET current abruptly. ➡ No need for comparator Single-electron processes are detected with SET. ➡ No need for differential amplifier

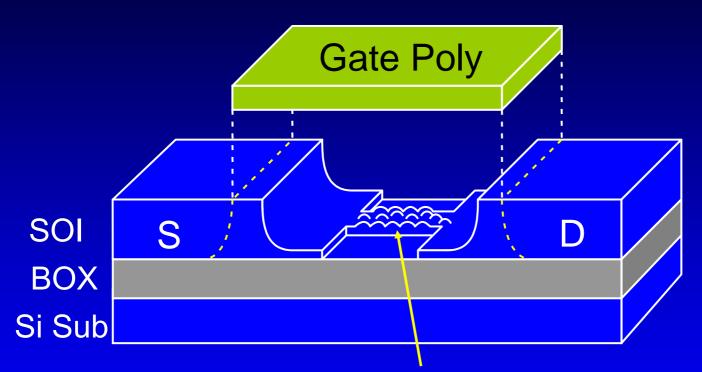

#### **Device Structure**

Ultrathin (< 2.5 nm) SOI film whose surface was undulated by alkaline-based solutions.

K. Uchida et al., DRC 1999, p138.K. Uchida et al., IEDM 2000, p863.K. Uchida et al., J. Appl. Phys. 90 (2001) 3551.

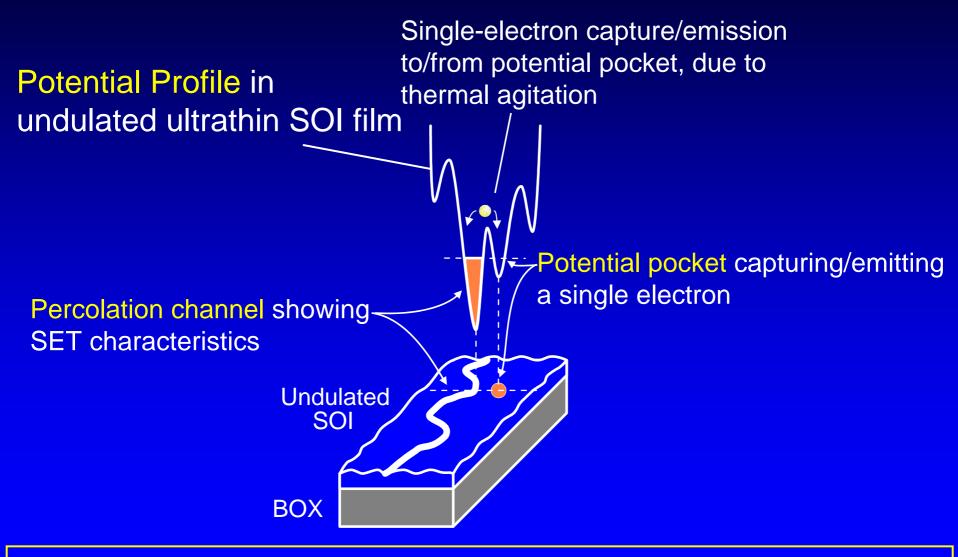

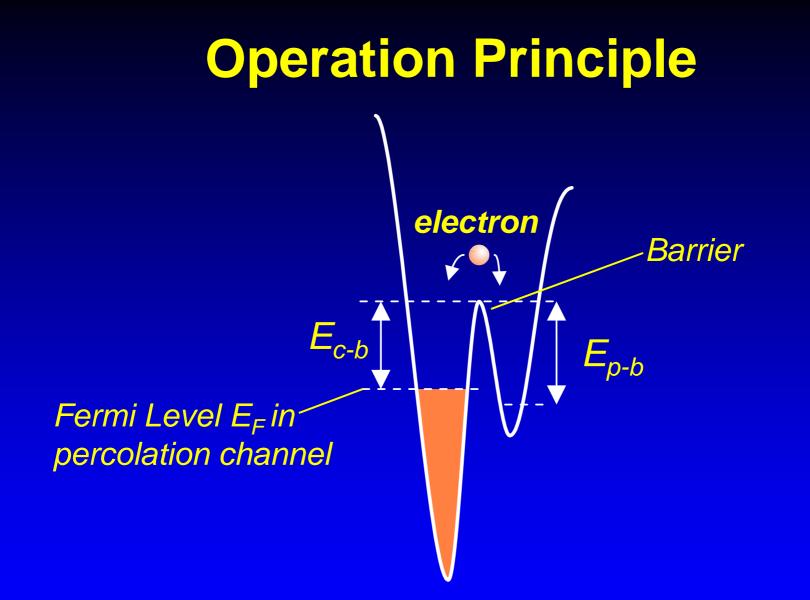

#### **Potential Profile**

Both an SET and a potential pocket are formed in the film<sub>6</sub>

At the moderate gate voltage, single-electron capture/emission can be observed frequently.

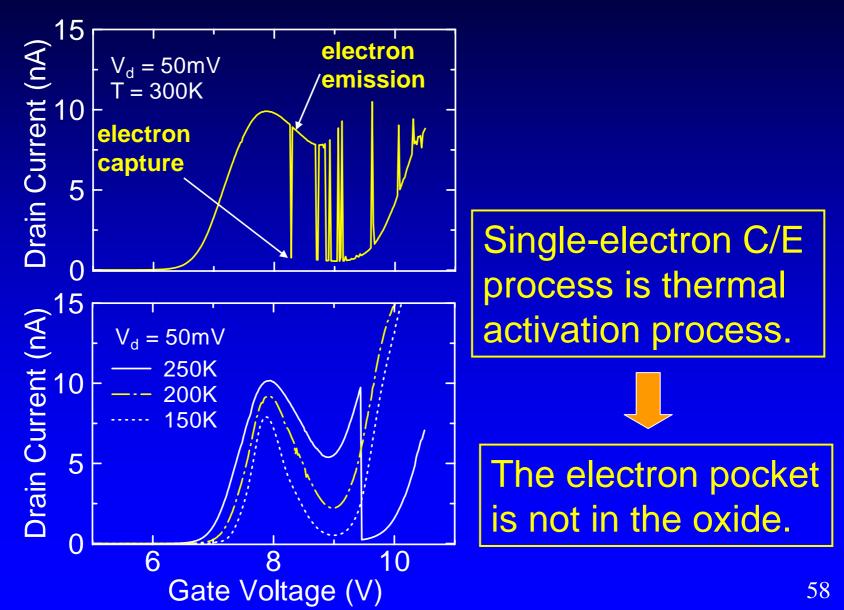

$I_d - V_g$  Characteristics

### Time Dependence of $I_d$

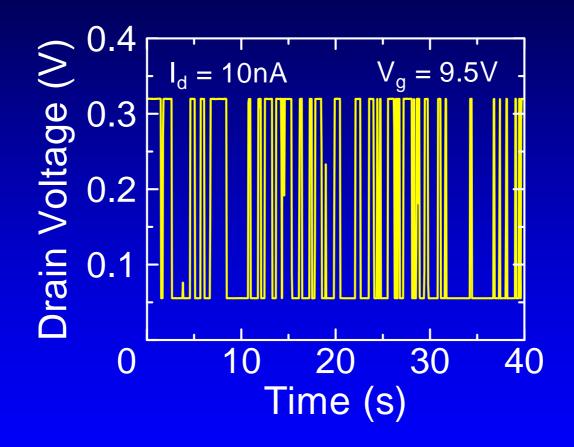

### Time Dependence of $V_d$

No need for high-gain amplifier.

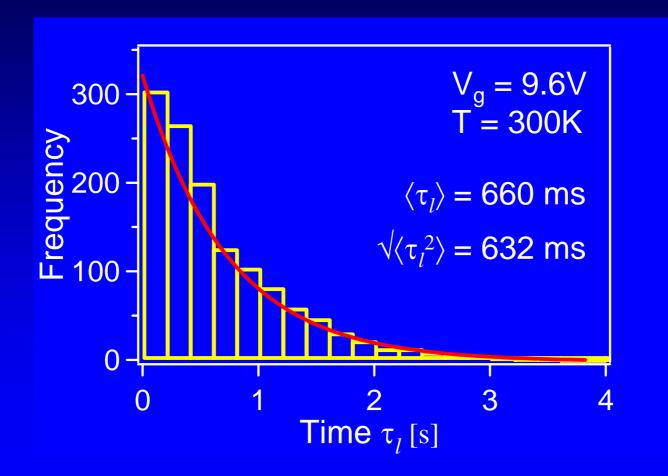

### **Distribution of low time (\tau\_{l})**

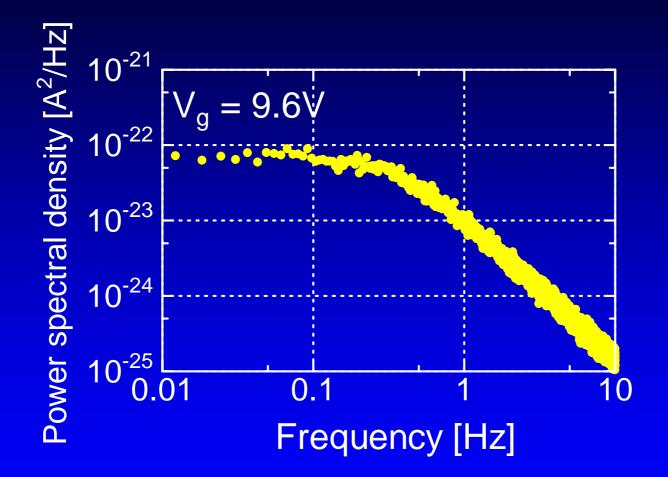

#### Power Spectrum Density of *I*<sub>d</sub>

Single-electron C/E process is a stochastic process (Poisson process).

#### Results of Tests for Random Number -Tests for Re-Sampled Data-

|                | Test               | Pass<br>Condition | Noise-based RNG                                | This Work                                    |

|----------------|--------------------|-------------------|------------------------------------------------|----------------------------------------------|

| FIPS PUB 104-2 | Monobit            | 9655 - 10346      | 10059 Pass!                                    | 10043 <b>Pass</b> .                          |

|                | Poker              | 2.16-46.17        | 10.23 <b>Pass!</b>                             | 15.88 <b>Pass</b> .                          |

|                | Longest Run        | 1 - 33            | 15 <b>Pass!</b>                                | 14 <b>Pass</b> .                             |

|                | Runs of length 1   | 2267 - 2733       | [0] 2588 <b>Pass!</b><br>[1] 2564 <b>Pass!</b> | [0] 2462 <b>Pass</b><br>[1] 2409 <b>Pass</b> |

|                | Runs of length 2   | 1079 - 1421       | [0] 1282 <b>Pass!</b><br>[1] 1246 <b>Pass!</b> | [0] 1243 <b>Pass</b><br>[1] 1296 <b>Pass</b> |

|                | Runs of length 3   | 502 - 748         | [0] 610 <b>Pass!</b><br>[1] 650 <b>Pass!</b>   | [0] 647 <b>Pass</b><br>[1] 586 <b>Pass</b>   |

|                | Runs of length 4   | 223 - 402         | [0] 302 <b>Pass!</b><br>[1] 327 <b>Pass!</b>   | [0] 290 <b>Pass</b><br>[1] 329 <b>Pass</b>   |

|                | Runs of length 5   | 90 - 223          | [0] 148 <i>Pass!</i><br>[1] 139 <i>Pass!</i>   | [0] 147 <b>Pass</b><br>[1] 177 <b>Pass</b>   |

|                | Runs of length 6+  | 90 - 223          | [0] 144 <b>Pass!</b><br>[1] 148 <b>Pass!</b>   | [0] 166 <b>Pass</b><br>[1] 158 <b>Pass</b>   |

| NIST SP 800-22 | $\chi^2$           | >0.05             | 0.140 <b>Pass!</b>                             | 0.648 <b>Pass</b>                            |

|                | Run                | >0.01             | 0.153 <b>Pass!</b>                             | 0.556 <b>Pass</b>                            |

|                | Freq. within block | >0.05             | 0.744 <b>Pass!</b>                             | 0.508 <b>Pass</b>                            |

|                | Freq.              | >0.05             | 0.275 <b>Pass!</b>                             | 0.085 <b>Pass</b>                            |

|                | Serial             | >0.05             | 0.106 <b>Pass!</b>                             | 0.693 <b>Pass</b>                            |

|                | Serial Correlation | -0.023 - 0.022    | -0.016 <b>Pass!</b>                            | 0.006 <b>Pass</b>                            |

|                | Poker              | >0.05             | 0.306 <b>Pass!</b>                             | 0.703 <b>Pass</b>                            |

|                | Gap of '1'~'16'    | >0.05             | <b>Pass all!</b> 0.08 - 0.90                   | <b>Pass all</b><br>0.15 - 0.94               |

The score of the single-electron RNG is comparable to or even superior to that of the stat-of-the-art high-quality RNG.

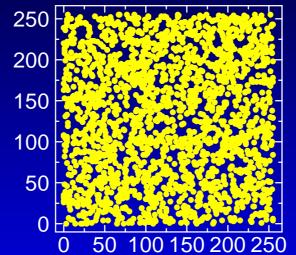

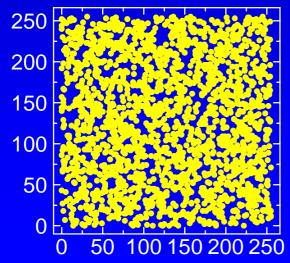

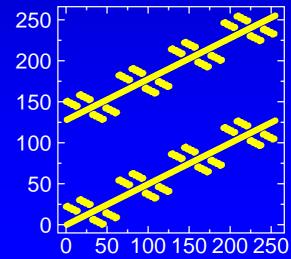

#### **Self-Correlation Plots**

#### **Single-electron RNG**

#### Thermal-noise-based RNG

#### Pseudo RNG (LFSR)

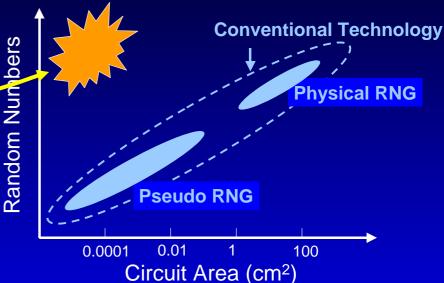

#### **Advantage of Single-Electron RNG**

# Schottky Source/Drain MOSFETs

# Introduction

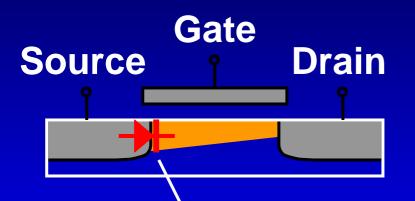

#### Schottky source/drain MOSFETs

- Simple fabrication

- > Low electrode resistances

- Better short-channel effect control

- > Excellent junction abruptness

**Schottky barrier** at source / channel interface significantly lowers the driving current.

#### In this study...

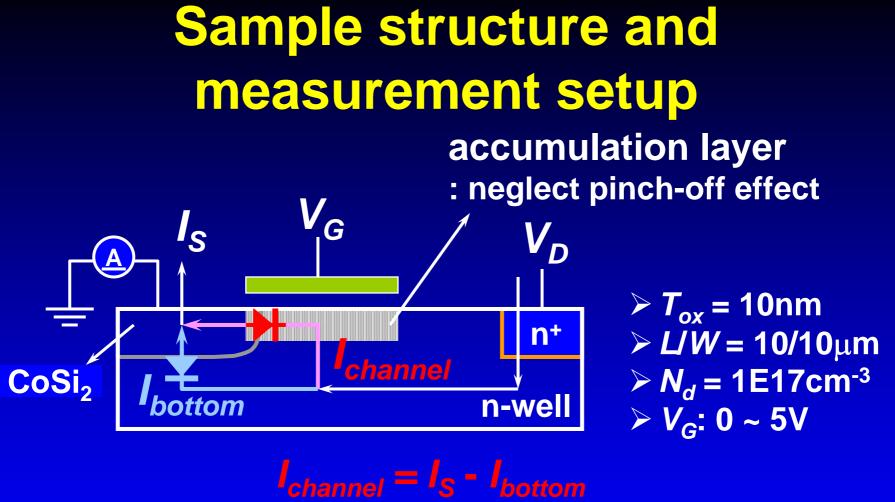

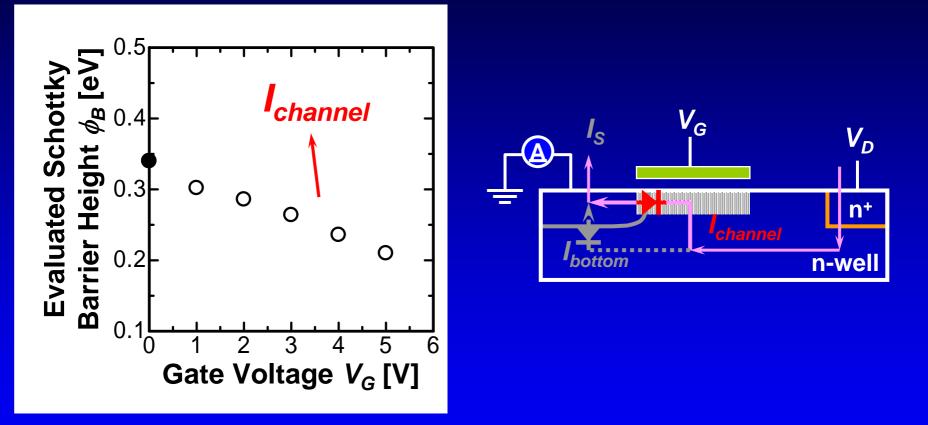

Effect of gate voltage on Schottky barrier height  $\phi_B$  is thoroughly investigated.

A. Kinoshita et al., SSDM 2003 67

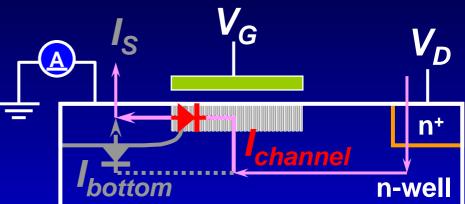

$(I_{bottom} \equiv I_S \text{ at } V_G: \text{ OV})$

Gate modulation current (*I<sub>channel</sub>*) can be extracted by subtracting *I<sub>bottom</sub>* from *I<sub>S</sub>*. A. Kinoshita et al., SSDM 2003 68

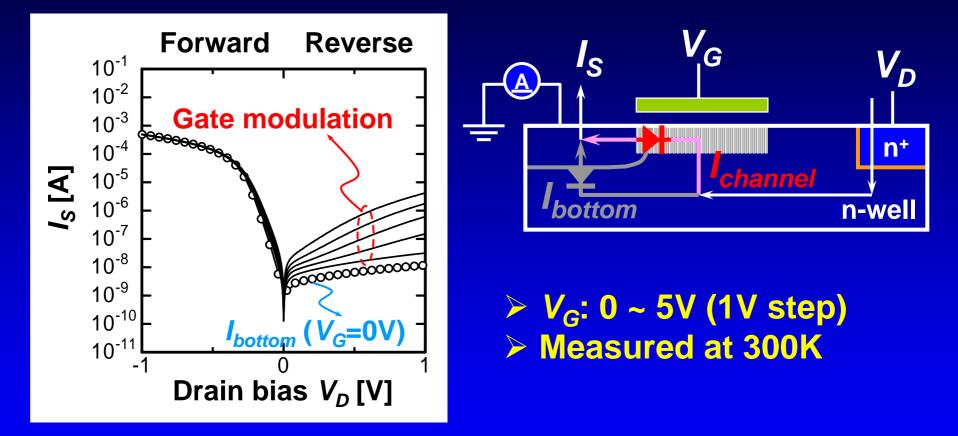

# Measured I<sub>s</sub> characteristics

V<sub>G</sub> strongly modulates reverse current of the surface Schottky diode.

A. Kinoshita et al., SSDM 2003 69

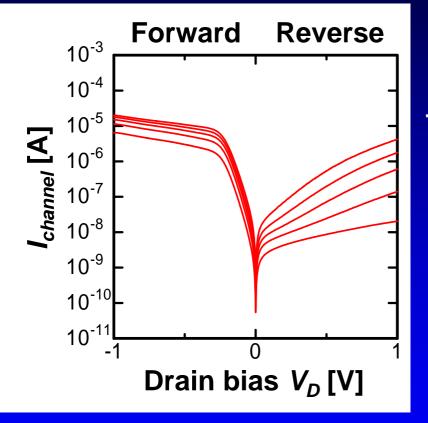

# Extracted I<sub>channel</sub> characteristics

*V<sub>G</sub>*: 1 ~ 5V (1V step)

Measured at 300K

Gate modulation current (*I<sub>channel</sub>*) is successfully extracted. A. Kinoshita et al., SSDM 2003 70

### Evaluated Schottky barrier height

First experimental evidence of barrier height lowering due to gate electrical field.

A. Kinoshita et al., SSDM 2003 71

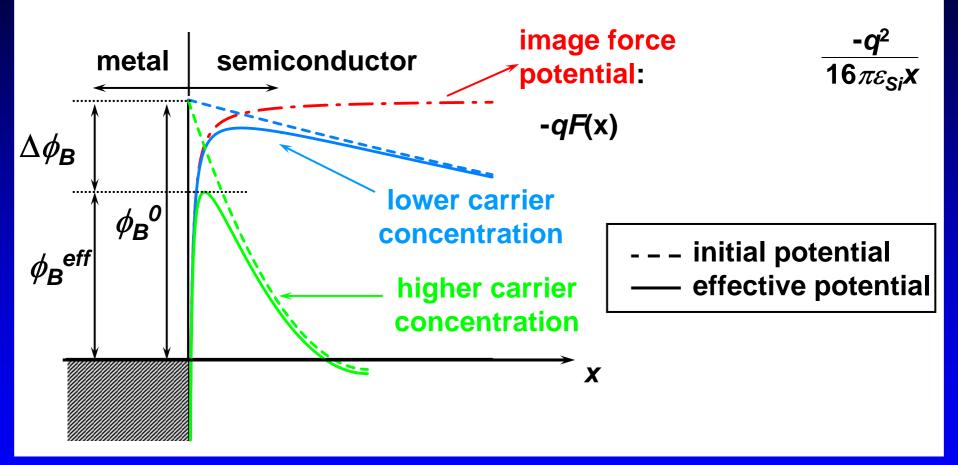

# Image force potential

Effective Schottky barrier height can be modulated by carrier concentration A. Kinoshita et al., SSDM 2003 72

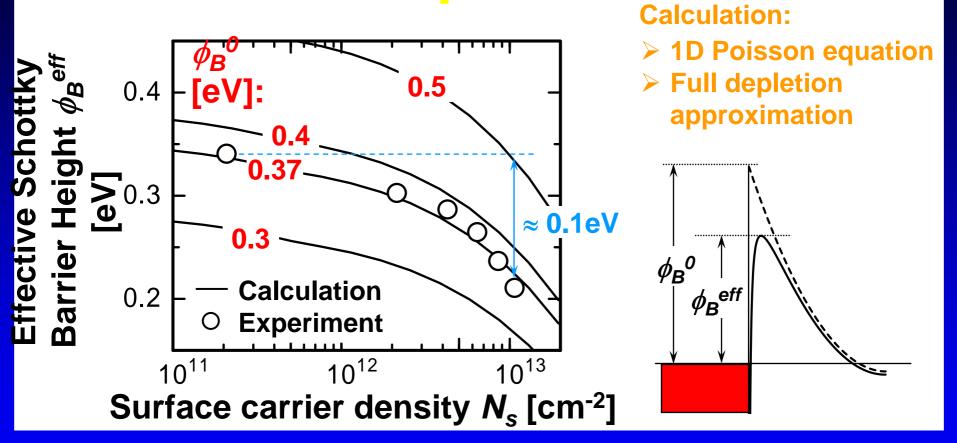

# $\phi_{B}$ lowering due to image force potential

Good agreement of the calculated and experimental results suggests image force potential is the origin of the gate induced barrier height lowering.

A. Kinoshita et al., SSDM 2003 73

### Conclusions

- In nanodevice era, we will encounter a number of challenges. However, if we can deal with those challenges, we will have new opportunities.

- In Ultrathin-body MOSFETs, quantum mechanical effects are very important. The QM effects offer us subband structure engineering.

- It is difficult to fabricate LSI of Single-Electron Devices. However, one single-electron device might enhance the security of LSI chips.

- In Schottky Source/Drain MOSFETs, Schottky brier at the source side plays a crucial role. However, the source side barrier might offers us another opportunity.